临海市尊龙凯时人生就是搏!官网,尊龙凯时人生就博官网登录,尊龙凯时人生就是真空设备有限公司

电话:0576-85021388/85138880

传真:0576-85021389

联系人:罗朝金13757699803

网址:http://lybeisite.com

地址:浙江省临海江南街道花溪路下岙余

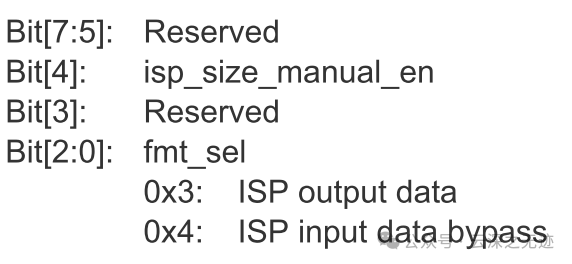

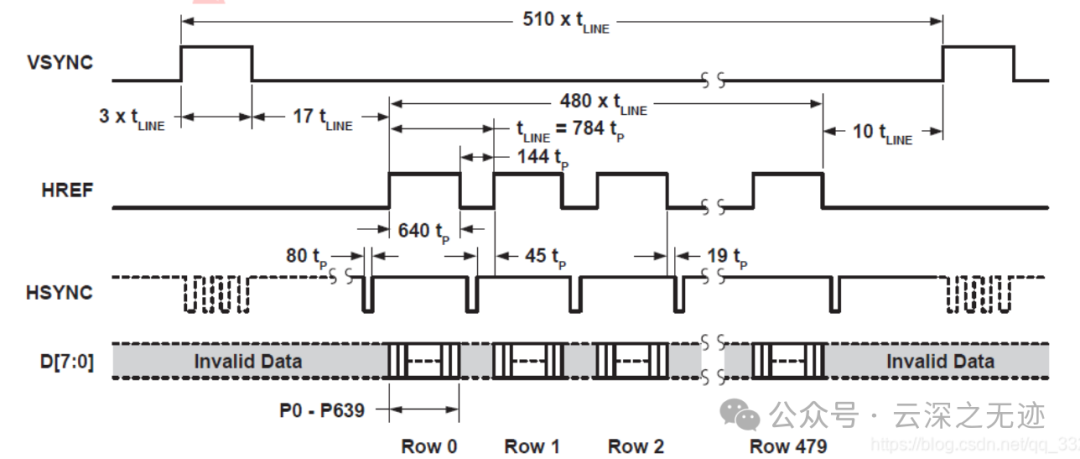

格式(我没有找到具体是什么)的像素数据★。像素数据依次传输★★★,每传输完一行数据时★★,行同步信号href会输出一个电平跳变信号★★,每传输完一帧图像时★,VSYNC会输出一个电平跳变信号。

al Signaling)电气接口标准,通常需要使用更多的电源和地线来支持高速数据传输。这使得dvp接口的设计更为复杂★,并且需要更多的空间来布线。DVP接口一个PCLK周期可以传输1by

所以都是:桥接处理器(同步输出),数字信号将被图像信号处理器(ISP)处理★,最后输出图像数据。

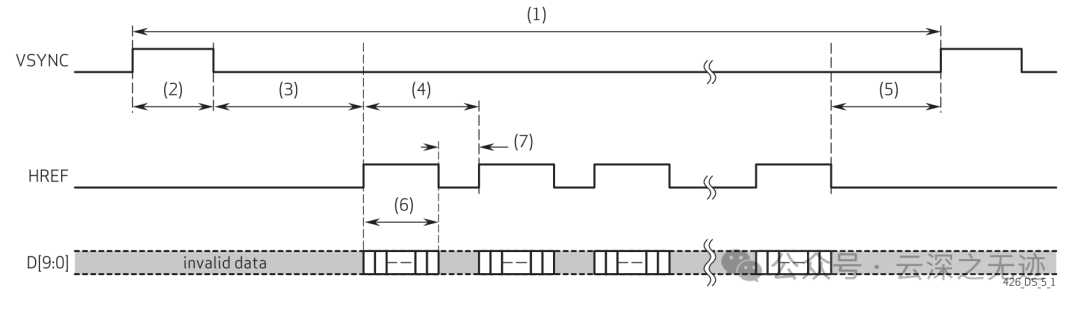

(2): VSYNC 信号内部★,代表帧开始前的时间间隔,通常称为垂直前沿★。

同步曝光:关于 FSIN 引脚用于同步曝光的功能,可以通过外部信号来同步多个摄像头的曝光时间★★★,确保它们捕获图像的时刻是一致的。要实现这一点需要在设计中额外添加对 FSIN 信号的支持,以确保能够正确地控制和同步曝光★★★。 内部时钟★★:由于每个图像传感器的时钟是自由运行的★★,同步曝光仅同步它们的曝光起点,而不会同步内部时钟或其他电路。这意味着即使曝光是同步的★★★,传感器间的像素数据输出可能仍存在微小的时差,这通常可以通过后续的软件处理来校正★★。

在一帧图像内部,每当 href 信号为高电平时,对应的行像素数据被视为有效。 D[9:0](数据线)★★: 传输图像数据的线。数据通常是在 href 高电平期间有效★★★,并且在 VSYNC 低电平期间不断传输以构成一帧图像。

手册 /

嵌入式学习-飞凌嵌入式ElfBoard ELF 1板卡-初识设备树之设备树组成和结构

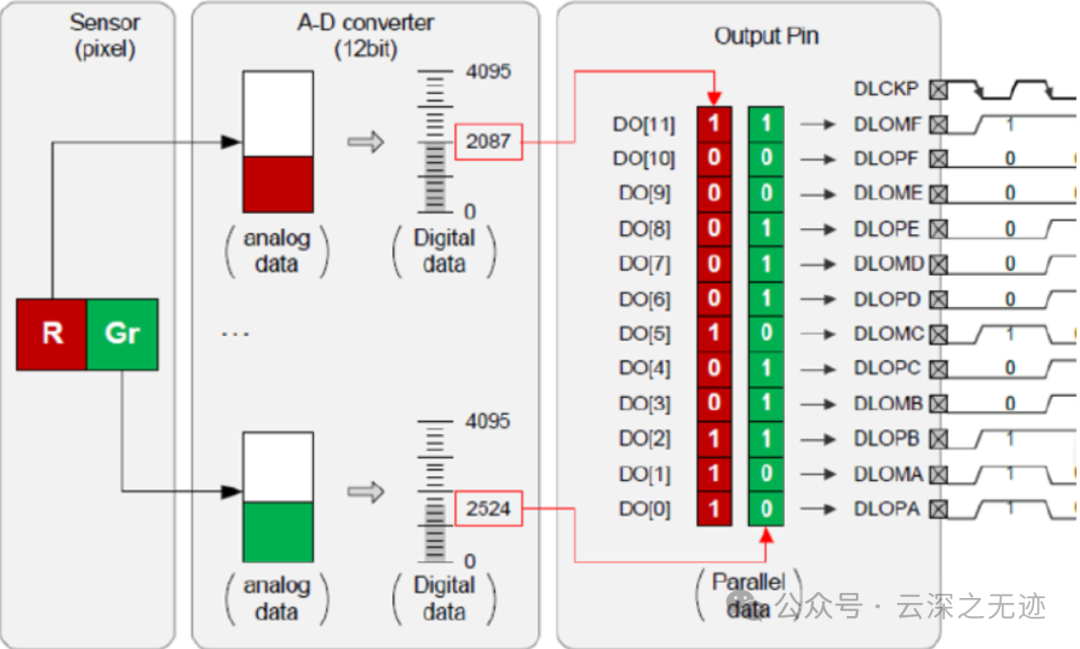

数据,1byte各位并行输出★★,一行Pixel输出完后★★★,Sensor输出一个HSYNC行同步信号,一帧所有行输出完成后,输出一个VSYNC帧同步型号★★。PCLK★★、D0、D1都是高频信号线(低位变化更加频繁),Layout时注意屏蔽干扰、不可与其它高频线并排或重叠走线)隔开。

DVP的协议吧,一般都认为是和VGA的协议差不多:只是VSYNC信号高低电平相反了★★。DVP协议的href信号是在HE

VSYNC(垂直同步): 指示一帧图像的开始和结束★★。在图中,一个 VSYNC 脉冲代表一帧图像的时间跨度★。 href(水平参考): 用于标示一行像素的开始和结束。

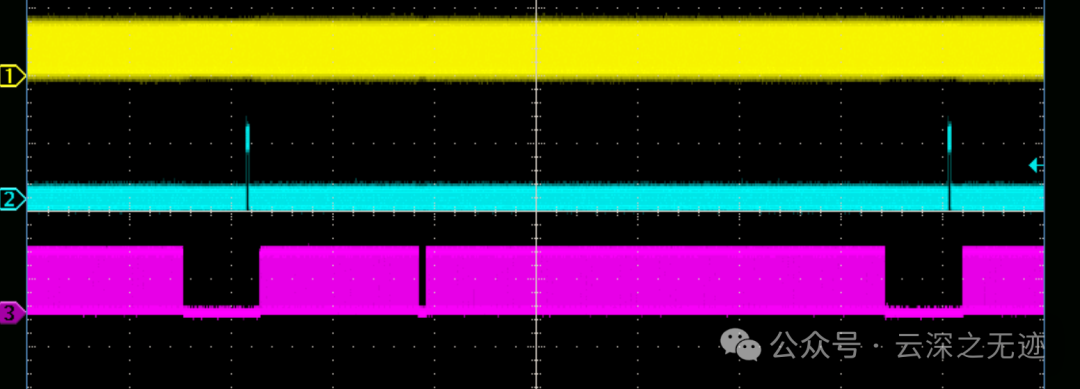

抓取的实测的 DVP 波形,黄色是输入时钟 ★★★,蓝色是帧同步信号 ★,红色是 PCLK(像素时钟)

ECU 的IP 核设计★。该IP 核基于RISC 技术的单指令、单周期的体系结构,并采用了自顶向下(top-down)的设计方法和

(6): href 信号内部,代表一行像素开始前的时间间隔,通常称为水平前沿。

为高电平是直接输出像素数据,而VGA接口的HSYNC信号在HSYNC为高时先后输出显示后沿★★★、有效图像数据、显示前沿。

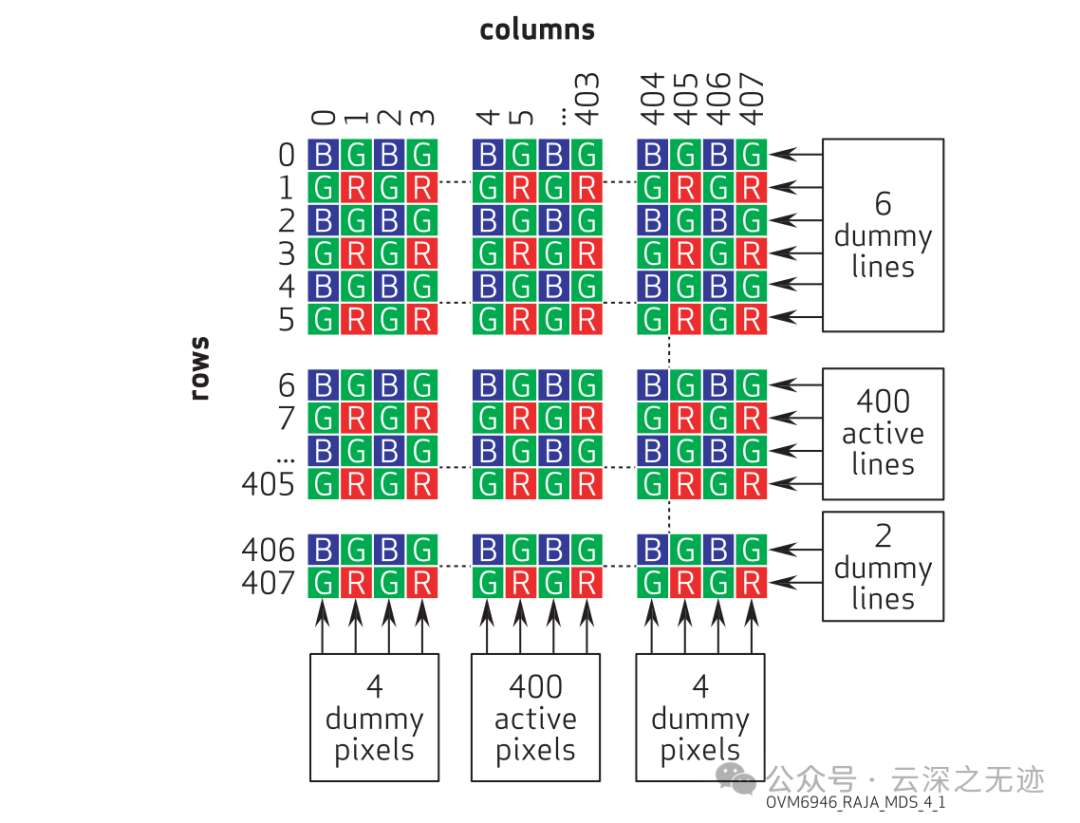

输出图像时,一帧帧地输出,在帧内的数据一般从左到右,从上到下★, 一个像素一个像素地输出★。

原理图 /

器,包括MC68HC9S12DP256和MC68HC08GZ32★★,分别用于

AEC 功能通过自动调整图像传感器的曝光时间来控制进入传感器的光量,确保图像既不过曝也不欠曝★。

系统中的应用 /

但是所有的方案都是流式处理★★,对于图像处理来说★★,永远都是等着前一级的处理完才能干活。

本文首先对列车通信网络体系结构★★★、wTB与姗两层通信网络等 内容进行了分析研究★,在此基础上,讨论了列车通信网的数据差错

AGC 功能通过调整图像传感器的增益来控制图像的亮度。增益可以被视为图像信号的放大系数。

已发展至接近其技术和应用极限,汽车工业正面临新的设计挑战★★,本文介绍FPGA在赛车引擎

数据线个像素同步时钟PCLK的驱动下发送1字节的数据信号★★,所以2个PCLK时钟可发送1个

(3): 有效的帧传输时间,这时候 href 和 D[9:0] 会传输有效的图像数据★★★。

设计 /

电路图 /

(1): 整帧的周期,从一个 VSYNC 的下降沿到下一个下降沿。(看着是上升沿)

文章出处★:【微信号:TT1827652464,微信公众号★:云深之无迹】欢迎添加关注★★!文章转载请注明出处。

采用 LLC 拓扑结构设计隔离式栅极驱动器电源,低成本 LLC 转换器的设计指南

(7): 有效的行传输时间★★★,在此期间★★★,D[9★:0] 上会传输有效的像素数据★★。 图中的 invalid data 注释指出在 VSYNC 信号为高时★,href 可能仍为高电平,但此时的数据不应被视为有效图像内容。